Cadence dévoile Virtuoso Advanced-Node pour les technologies de fabrication en géométrie de 10 nm

-

Domains:

- Development plan

-

Domains:

- Development plan

San Jose, Californie, le 1er décembre 2015

Cadence Design Systems, leader mondial en matière d’innovation en conception électronique, annonce la disponibilité de sa nouvelle plate-forme Virtuoso Advanced-Node destinée à toutes les conceptions avancées FinFET en géométrie 10 nm. Cette plate-forme de conception sur-mesure de nouvelle génération multiplie par 5 la productivité des concepteurs tout en assurant la prise en charge des technologies émergentes en 7 nm.

Les capacités innovantes de la plate-forme Cadence Virtuoso Advanced-Node permettent aux concepteurs en technologie FinFet sur nœuds avancés de mieux gérer la complexité ainsi que les effets du procédé de fabrication.

Les principales fonctionnalités de cette plate-forme sont les suivantes :

- Conception multi-motifs (multi-patterning design) et sensible au coloriage: supporte la décomposition des couches à 4+ motifs, augmentant la productivité via l’accès aux différentes possibilités de coloriage;

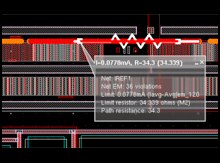

- Conception validée électriquement (EAD — Electrically Aware Design): permet aux concepteurs de traiter les effets parasites et d’électromigration (EM) d’un bout à l’autre du cycle de conception, sans attendre que la conception soit achevée, réduisant ainsi jusqu’à 30 % le délai de conception;

- Flot de conception basé sur les générateurs de modules (ModGen) de matrices de composants: supporte le routage local et indépendant de ces modules, réduisant considérablement les itérations de conception et multiplie par 25 la productivité;

- Routage sur-mesure en 10 nm: prise en charge de nouvelles règles de dessin, ce qui simplifie grandement la phase d’implémentation physique et minimise la possibilité d’erreur de coloriage qui présente un risque de diffusion lors de la conception en géométrie 10 nm;

- Système de vérification physique en cours de conception (iPVS —In-design Physical Verification System) : permet aux ingénieurs en charge du layout de détecter et corriger instantanément les erreurs au cours de l’implémentation, avec à la clé une réduction significative des erreurs liées aux règles de dessin et une amélioration de la productivité globale des concepteurs de l’ordre de 15 %.

Pour plus d’informations sur la plate-forme Virtuoso Advanced-Node optimisée pour la technologie 10 nm, visitez le site rendez-vous sur cette page.

Plus sur Cadence : www.cadence.com